# **VLSI Testing using FPGA Devices**

M. K. Stojcev, I. Ž. Milovanovic, E. I. Milovanovic, T. R. Nikolic\* Faculty of Electronic Engineering Niš Serbia

**ABSTRACT:** For VLSI testing, the Built-in-self-text is popularly deployed. To get a high fault coverage in run test vectors, a linear feedback shift register is used to test. In this paper we have used parallel LFSR to experiment the intellectual property blocks with VLSI. The PLFSR is input is linked to apply intest mod test vectors which, possible, detect faults. The proposed PLFSR is implemented FPGA device, and perform at 200 MHz clock frequency and finally produced two random numbers per clock period. The design generated is reconfigurable and can operate with different primitive. he design we have developed shown better trade off performance which has high system throughput and achieve less power consumption.

Keywords: Built-In Self-Test, Linear Feedback Shift Register, Random Number Generator, FPGA Design

Received: 29 January 2022, Revised 29 April 2022, Accepted 4 May 2022

DOI: 10.6025/jic/2022/13/3/67-74

**Copyright:** with Authors

### 1. Introduction

Random numbers, RNs, are used today in numerous applications including electronic circuit testing, cryptography, simulations of wireless communication systems, Monte Carlo simulations, etc.[1]. Two basic approaches are used to generate RNs. The first one is based on measurement phenomenon of some physical process which is completely unpredictable such as thermal noise in electronic circuits, or noise-power level in radio-frequency receivers. Random number generators, RNGs, which use this principle of operation can be implemented using analogue and digital electronics, but these design solutions tend to be expensive and slow. The second approach uses computational algorithms that generate long sequences of apparently RNs. In this case RNs can be generated both by using software algorithms that involve complex mathematical operations and relatively slow RN sequences generation, and by using hardware which can implement less complex methods but fast RNs generation [2]. Up-todate complex VLSI CMOS ICs run in the range from several hundreds MHz up to several GHz, so implementation of low-price, high-speed and simple RNG becomes an ultimate design goal. The RNG as electronic device is designed to generate a sequence of numbers that lack any pattern. But in practice it is very difficult, or almost impossible, to generate a series of logical steps that produce numbers that do not follow some definite sequence. These RNs are called pseudo random numbers, PRNs.

There are two different hardware implementations of pseudo random number generators, PRNGs, that are widely used for logic built-in-self-test, BIST, applications [3]. The first one is based on usage of linear feedback shift register, LFSR. Its structure is simple, suitable for implementation as IP core within a complex VLSI ICs, and therefore is most commonly used to generate test

Journal of Intelligent Computing Volume 13 Number 3 September 2022

patterns or test sequences [5-8]. The second design uses cellular automata, CA. The CA based PRNGs are more complex devices but provide patterns that look more random [2-3]. In this paper we have presented an efficient parallel pseudo random number generator based on LFSR (PLFSR) which is used for fast testing the constituents (IP cores) within a complex VLSI circuits. In respect to the parallel implementations of LFSR, described in [9-10], the proposed design characterizes higher system throughput and reconfigurability.

The rest of the paper is organized as follows. In section two a brief description of standard LFSR generators is given. Section 3 deals with principle of operation and structure of parallel LFSR generator. We start with mathematical background. After that we describe PLFSR hardware structure at block diagram level. Experimental results are given in Section 4. Concluding remarks are given in Section 5.

# 2. Standard LFSR Generators

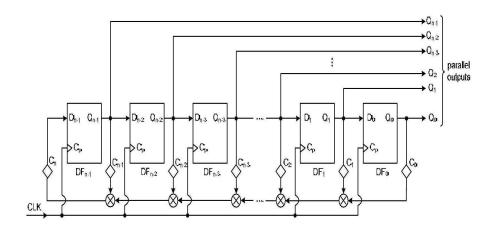

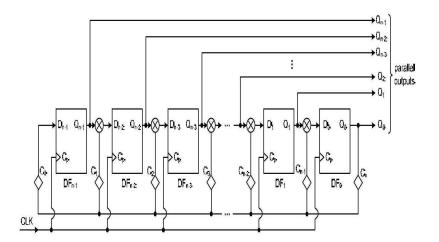

LFSR belong to the devices known as finite state machines. Its input state is a linear function of the pervious state. By using feedback it modifies itself on each rising edge of the clock. The L-bit initial value of LFSR is called seed, where L is called its length, and the bit position that affects next state is called tap. Two different LFSR implementations exist. The Fibonacci configuration (also known as external-XOR LFSR) consists of a simple shift register in which a binary-weighted modulo-2 sum of taps is fed back to the input , Fig. 1. The Galois implementation (alternatively called internal-XOR LFSR) consists of shift register, the contents of which are modified at every step by a binary-weighted value of the output stage, Figure 2.

Figure 1. Fibonacci implementation of LFSR

Figure 2. Galois implementation of LFSR

Codes generated by any of the two aforementioned types of LFSR are actually pseudo-random sequences because the sequence, known as the period of the PRNG, repeats after a certain number of clock cycles. Once it reaches its final state, it will traverse the sequence exactly as before. The advantage of serial LFSR architecture is small amount of hardware it requires. With aim to increase the throughput of the LFSR generator, we propose a LFSR that generate *k* consecutive pseudo random numbers in parallel (PLFSR).

### 3. Parallel LFSR Generator

#### 3.1. Mathematical background

Let

$$P_n(x) = c_0 x^0 + c_1 x^1 + \dots + c_{k-1} x^{k-1} + c_k x^k + \dots + c_n x_n$$

(1)

be a feedback polynomial of degree n. The polynomial (1) has the following property

$$c_0 = c_n = 1$$

,  $c_i = \{0,1\}$ , and  $c_1 = c_2 = \cdots = c_{k-1} = 0$ .

In order to generate pseudo random number sequence of length n, polynomial (1) has to be a primitive one (see for example [4]).

Let

$$\vec{Q}(0) = [q_1^{(0)} \quad q_2^{(0)} \quad \dots \quad q_n^{(0)}]^T$$

Be a vector that corresponds to the initial state of the LFSR characterized by the polynomial (1). The next state of the LFSR can be obtained from

$$\vec{Q}(1) = A \oplus \vec{Q}(0)$$

where

$$A = \begin{bmatrix} c_1 & c_2 & \dots & c_{n-1} & 1 \\ 1 & 0 & \dots & 0 & 0 \\ 0 & 1 & \dots & 0 & 0 \\ \vdots & & & & \\ 0 & 0 \dots & 0 & 1 & 0 \end{bmatrix}$$

is an  $n \times n$  matrix joined with polynomial (1), and  $\oplus$  a logical exclusive-or operation. In general, i-th state of the LFSR as a function of the initial state can be obtained according to

$$\vec{Q}(i) = A^i \oplus \vec{Q}(0), \text{ where } A^i = A \oplus A^{i-1}$$

Since  $c_1 = c_2 = \ldots = c_{k-1}$ , we can generate k consecutive pseudo random numbers in parallel, while keeping the same computational complexity for each of k feed-back results.

We will explain the idea on the example of the polynomial

$$P_5(x) = 1 + x^3 + x^5 \tag{2}$$

Matrix that corresponds to polynomial (2) is

|     | 0 | 0 | 1 | 0 | 1                     |

|-----|---|---|---|---|-----------------------|

|     | 1 | 0 | 0 | 0 | 0                     |

| A = | 0 | 1 | 0 | 0 | 0                     |

|     | 0 | 0 | 1 | 0 | 0                     |

|     | 0 | 0 | 0 | 1 | 1<br>0<br>0<br>0<br>0 |

Let  $\vec{Q}(0) = \begin{bmatrix} q_1^{(0)} & q_2^{(0)} & q_3^{(0)} & q_4^{(0)} & q_5^{(0)} \end{bmatrix}^T$  the initial state of the LFSR characterized by (2). The next four states can be obtained according to the following

$$\vec{Q}(1) = A \oplus \vec{Q}(0) = \begin{bmatrix} 0 & 0 & 1 & 0 & 1 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{4}^{(0)} \\ q_{5}^{(0)} \end{bmatrix} = \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{4}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{4}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{3}^{(0)} \\ q_{4}^{(0)} \\ q_{5}^{(0)} \end{bmatrix} = \begin{bmatrix} q_{2}^{(0)} \oplus q_{4}^{(0)} \\ q_{3}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{4}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{2}^{(0)} \oplus q_{4}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{2}^{(0)} \oplus q_{4}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{2}^{(0)} \\ q_{3}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{1}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \end{bmatrix}^{2} \oplus \begin{bmatrix} q_{1}^{(0)} \\ q_{1}^{(0)} \\ q_{5}^{(0)} \\ q_{5}^{(0)} \\ q_{6}^{(0)} \\$$

According to the above equations we can conclude that computational complexity of determining states  $\vec{Q}(1)$ ,  $\vec{Q}(2)$  and  $\vec{Q}(3)$  is the same. On the other hand, determining state  $\vec{Q}(4)$  requires two XOR operations for computing element  $q_1^{(4)}$ , leading to computational imbalance.

# 3.2. Parallel LFSR implementation

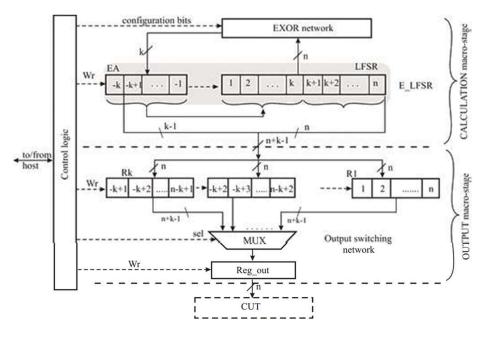

For the given feedback polynomial we propose LFSR for parallel generation of *k* consecutive pseudo random numbers, called parallel LFSR (abbreviated as PLFSR), shown in Figure 3.

Figure 3. The structure of PLFSR

# PLFSR consists of the following building blocks:

- Extended parallel shift register (E\_LFSR) with n+k cells (flip-flops). The right most *n* cells correspond to the standard LFSR, while the *k* leftmost cells represent linear array of *k* individual cells, called extension array (EA)

- The EXOR network is a combinatorial network of EXOR circuits which generate k product terms in parallel that feed in EA. Constituents of EXOR network are configuration registers that are used for selecting the primitive polynomial and the length of  $E\_LFSR$ .

- k registers, R1 to Rk, composed of n flip-flops, used for temporal storing of k consecutive states of PLFSR

- Output switching network (MUX), which operates as k-input multiplexer.

- Output register, Reg\_out, output stage used for driving Circuit Under Test (CUT)

Control logic (CL) used to generate control signals for driving the constituents of PLFSR.

The PLFSR is implemented as two-macro-stage pipeline. Within the first macro-stage, called CALCULATION, k consecutive pseudo-random sequences are calculated in parallel. The CALCULATION stage operates as two-cycle logic. During the first cycle, the content of E\_LFSR is shifted for k positions right. In the second cycle, k consecutive resultant bits are calculated by EXOR network and written into EA. The second macro-stage, called OUTPUT stage, is implemented as k-cycle (poly phase) logic. During the first cycle registers R1 to Rk are loaded in parallel. In the next k cycles, k consecutive pseudorandom numbers are selected by MUX block and written into Reg\_out.

During system initialization configuration bits are loaded into EXOR network. This provides that the proposed PLFSR can implement any feedback polynomial of degree n. In a concrete case, primarily limited by the amount of available logic blocks and input-output capacity of FPGA chips, we can implement, using reconfiguration, any polynomial of degree  $n \le 32$ .

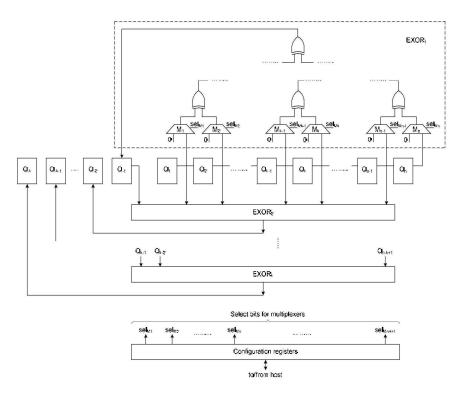

The most complex part of PLFSR is the EXOR network, shown in Figure 4. It consists of k reconfigurable EXOR blocks, each implemented as binary three of EXOR circuits. Multiplexers,  $M_1$  to  $M_n$ , are used to switch on/off a corresponding tap in the

feedback loop. The outputs of a configuration register are used for driving the select signals of multiplexers  $M_1$  to  $M_n$ . The propagation delay of EXOR network is equal to the propagation delay through one multiplexer, plus  $log_2 n$  delay through EXOR circuits. It is independent of the chosen feedback polynomial for the given n.

Figure 4. The structure of EXOR network

# 4. Experimental Results

In order to verify our design, we have implemented both PLFSR and standard LFSR in FPGA technology. For the sake of verification we have implemented PLFSR that generates two consecutive pseudo random sequences in parallel. The PLFSR and logics were described at register transfer level using VHDL. For FPGA implementation of PLFSR an LFSR we have used Xilinx development CAD tool ISE WebPack 13.1. Design verification was performed using test benches intended for excitation of PLFSR and LFSR. PLFSR and LFSR were implemented on FPGA devices from Virtex-6 LP series (circuit xc6vlx75tl-11f484). The obtained results are given in Table 1, for standard LFSR, and in Table 2 for PLFSR.

|             | No of<br>flip- | No of<br>occu- | Best<br>case    | Dynamic<br>Power | Quiescent<br>Power | Total<br>Power |

|-------------|----------------|----------------|-----------------|------------------|--------------------|----------------|

|             | flops<br>in    | pied<br>Slices | achie-<br>vable | (mW)             | (mW)               | (mW)           |

|             | LFSR           |                | (ns)            |                  |                    |                |

| Virtex6 LP  | 32             | 71             | 1.701           | 6.65             | 781.19             | 787.84         |

| xc6vlx75tl- | 24             | 52             | 1.885           | 5.99             | 781.18             | 787.17         |

| 1Lff484     | 16             | 38             | 1.888           | 5.62             | 781.17             | 786.80         |

|             | 8              | 18             | 1.722           | 4.51             | 781.16             | 785.67         |

Table 1. Implementation results for standard LFSR

|             | No of<br>flip- | No<br>of      | Best<br>case    | Dynamic<br>Power | Quiescent<br>Power | Total<br>Power |

|-------------|----------------|---------------|-----------------|------------------|--------------------|----------------|

|             | flops<br>in    | occu-<br>pied | achie-<br>vable | (mW)             | (mW)               | (mW)           |

|             | LFSR           | slices        | (ns)            |                  |                    |                |

| Virtex6 LP  | 32             | 113           | 1.883           | 11.17            | 781.26             | 792.43         |

| xc6vlx75tl- | 24             | 90            | 1.924           | 11.65            | 781.26             | 792.91         |

| 1Lff484     | 16             | 57            | 1.768           | 9.19             | 781.23             | 790.42         |

|             | 8              | 35            | 1.735           | 7.69             | 781.21             | 788.89         |

### Table 2. Implementation results PLFSR

According to the results given in Tables 1 and 2 we can conclude the following:

- Hardware overhead of PLFSR compared to the standard LFSR is from 50% (for the polynomial of degree 16) up to 94% (for the polynomial of degree 8). For the given polynomial degree n, hardware overhead is independent of the chosen polynomial, i.e. active taps.

- Dynamic power consumption depends of the chosen primitive polynomial. For both PLFSR and standard LFSR power consumption was estimated using the same polynomial. The dynamic consumption ratio between PLFSR and standard LFSR, varies from 1.63 (for the polynomial of degree 16) up to 1.94 (for the polynomial of degree 24).

- Contribution of dynamic power consumption to the total power consumption is approximately 1.5% which implies that the impact of the PLFSR hardware is very low with respect to the total hardware of the FPGA chip.

Note that the system throughput of the PLFSR is two times higher compared to the standard LFSR under the same operating conditions, e.g. system clock.

# 5. Conclusion

Random number generation is an important application area that is met in BIST devices for complex VLSI circuits. In this case it is essential that the random numbers generator be amenable to hardware implementation in terms of area, high throughput rate, low-power dissipation, and low complexity. LFSR are commonly used as pseudo test pattern number generators in low overhead BIST schemes. In this paper we have presented an efficient parallel pseudo random number generator based on LFSR which is used for fast testing the constituents (IP cores) within a complex VLSI circuits. The proposed scheme was implemented on VIrtex6 LP FPGA device (circuit xc6vlx75tl-11f484), running at clock speed of 200MHz, while delivering two 32-bit random numbers per clock. The reconfigurable hardware allows to implement any polynomial of degree 32. In comparison to standard pseudo random number generator based on LFSR, the proposed solution characterizes 2x higher throughput rate, at cost penalty of 94% of higher dynamic consumption and hardware overhead in the worst case.

### Acknowledgement

This work was supported by the Serbian Ministry of Education and Science, Project N0 TR-32009 – "Low power reconfigurable fault-tolerant platforms"

### References

[1] Random number generation (2013). Available. en.wikipedia.org/wiki/Random\_number\_generation.

[2] Wijesinghe, W.A.S., Jayananda, M.K. & Sonnadara, D.U.J. (2006) Hardware implementation of random number generators.

Journal of Intelligent Computing Volume 13 Number 3 September 2022

Proceedings of the Technical Sessions. Available at www.ip-sl.org/procs/ipsl063.pdf. Mart 2013, Vol. 22. Institute of Physics: Sri Lanka, pp. 25–36.

[3] Design for Testability, Laung-Terng (L.-T.) Wang, Chapter 3 Electronic design automation: Synthesis, verification, and test. In: (edited by L.-T. Wang, Y.-W. Chang & K.-T. (T.) Cheng). Morgan Kaufmann Publishers: Burlington, MA, USA, pp. 97–172.

[4] Jha, N. & Gupta, S. (2003). Testing of Digital Systems. Cambridge University Press: Cambridge.

[5] Nas, R.J.M. & van Berkel, C.H. (2010) High throughput, low setup time, reconfigurable linear feedback shift registers, *IEEE international conference on computer design (ICCD)*, pp. 31–37.

[6] Ahmed, N., Tehranipour, M.H. & Nourani, M. (2004) Low power pattern generation for BIST architecture. Proceedings of the 2004 International Symposium on Circuits and Systems (ISCAS'04), Vol. 2, pp. 689–692.

[7] Bezerra, E.A., Vargas, F. & Gough, M.P. (2001) Improving reconfigurable systems reliability by combining periodical test and redundancy techniques: A case study. *Journal of Electronic Testing*, 17, 163–174 [DOI: 10.1023/A:1011177911388].

[8] Jhansirani, A., Harikishore, K., Basha, F.N., Poornima, J., Jyothil, M., Sahithi, M. & Srinivas, P. (2012) Fault tolerance in bit swapping LFSR using FPGA architecture. *International Journal of Engineering Research and Applications*, 2, 1080–1087.

[9] Lowy, M. (1966) Parallel implementation of Linera Feedback Shift Registers for low power applications. *IEEE Transactions on Circuits and Systems. Part II: Analog and Digital Signal Processing*, 43, 458–466.

[10] Hamid, M.E. & Chen, C.-I.H. (1998) A note to low-power linear feedback shift registers. *IEEE Transactions on Circuits and Systems* II (trans. IEEE), 45, 1304–1307 [DOI: 10.1109/82.718599].