# **Self-Tuning Low Noise Amplifier During One Design Pattern**

Goran Jovanovic, Darko Mitic, Mile Stojcev and Tatjana Nikolic University of Niš, Faculty of Electronic Engineering Aleksandra Medvedeva 14, 18000 Niš Serbia, {goran.jovanovic, darko.mitic, mile.stojcev, tatjana.nikolic@elfak.ni.ac.rs}

**ABSTRACT:** We have carried out the self-tuning low noise amplifier which is normally termed as One design pattern. To equal the input signal frequency, we developed the phase control loop where the aim is to force the filter central frequency by changing the amplifier resonant. The LNA parameter has consistent maximum gain with good frequency and ensure full tuning for parameter perturbations. We have used the design of BICOMOS technology for confirming the LNA. The experimentation shows the full noise is optimum during the use of compression points.

Keywords: Low-noise Amplifier, Tunable, Phase Control Loop, Resonant Circuit

Received: 30 January 2022, Revised 3 June 2022, Accepted 17 June 2022

**DOI:** 10.6025/stj/2022/11/2/41-48

Copyright: with Authors

## 1. Introduction

An inherent problem in implementing analog circuits is that the values of manufactured analog circuit components often differ from the design specifications because of process parameters, supply voltage, and temperature (PVT) variations. Due to these perturbations, the practically obtained results are not optimal. For instance, even a 1% discrepancy from the central frequency is unacceptable to fulfill frequency accuracy requirements in intermediate frequency (IF) filters, which are commonly used in receivers. Other solutions to compensate variations of frequency characteristics due to PVT variations are based on utilization of tunable filters, master-slave filter tuning schemes and self-tuning filters [1-3, 7]. The latter approach, as more challenging one, is proposed in this paper.

Tunable selective amplifiers can be realized by using digitally controlled binary-weighted capacitor array, or current mirror array [2]. The switching scheme is based on successive approximation algorithm. However, the frequency accuracy with digital tuning is constrained by the number of tuning (not > 5) bits used. This is done in order to avoid too much overhead in chip area and to minimize the parasitic effects of switch resistances, resulting in 5-10% frequency mismatch [2].

Analog filters and selective amplifier are also adjusted by master–slave tuning schemes [3, 7]. The most commonly used master-circuit is voltage-controlled oscillator (VCO), whereas a slave filter is built with identical integrators. However, there are some difficulties in matching filter characteristics with characteristics of the master VCO [1]. Superior approach is to use voltage

controlled filter as a master, what results in better matching between master and slave filters.

Each selective LNA at characteristic frequencies (cut-off, central frequency etc.) has defined phase shifts values. By comparing the phases of input and output signals, it is possible to detect the mismatch of filter characteristics. In order to obtain the desired phase transfer function, self-tuning filters use the estimated phase error as correction factor. In our proposal, to accomplish phase error correction we use a phase control loop, similar to one used in tuning oscillators with phase locked loop (PLL), or delay lines with delay locked loop (DLL) [4, 5].

Here we present a LNA architecture, which belongs to a class of self-tuning circuits. Two benefits arise from the proposed solution: (i) the LNA is always tuned to input signal frequency, even in a presence of huge parameter perturbations, and (ii), the LNA can be used as a selective amplifier in wide range of input signal frequencies.

The paper is organized as follows. Section 2 concentrates on realization of the tunable LNA. The structure of self-tuning LNA with phase control loop is defined and described in the Section 3. Simulation results are presented in Section 4 and self-tuning LNA application in Section 5. Finally, Section 6 contains some concluding remarks.

## 2. A Tunable Narrowband Low-noise Amplifier

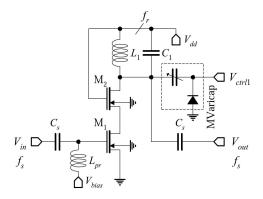

The LNA schematic, used in this paper, is based on one of the most popular topologies, known as inductively degenerated common source LNA [8]. The simplified circuit given in Figure 1 (without bias and matching circuits) is composed of two MOS transistors,  $M_1$  and  $M_2$ , LNA amplifier scheme. MOS transistor  $M_1$ , operates as common-source. The inductor  $L_{pr}$  is connected to a DC biasing node. The Miller effect for LNA circuit is very important. This effect strongly limits its frequency characteristics and provides poor reverse isolation. A cascode transistor  $M_2$  operates in common-gate mode. It significantly decreases the Miller effect. By using two active elements,  $M_1$  and  $M_2$ , high LNA gain is obtained.

The output load is implemented as resonant circuit consisting of  $L_1$ ,  $C_1$  and MVaricap. The voltage drop over the load is lower than the drop over a resistive load of the same impedance. This solution provides correct circuit operation at lower power supply voltage level ( $V_{dd} = 2.7 \text{ V}$ ), and has lower power dissipation.

MVaricap element corresponds to voltage controlled capacitor. In IHP BiCMOS technology, it is implemented as modified PMOS transistor [6]. By controlling polarization voltage of a N-well the capacitance between gate and channel of PMOS transistor varies. The value of a control voltage,  $V_{ctrl}$  determines a capacitance of MVaricap element, so the resonant frequency,  $f_r$ , is given as

$$f_r = \frac{1}{2\pi\sqrt{L_1(C_1 + C_{\text{MVaricap}})}} \tag{1}$$

The dynamic impedance of a resonant circuits, at  $f_{\nu}$ , is very high so that the LNA has very high gain, too.

Figure 1. Low-noise amplifier scheme

Elements of resonant circuit a selected in such way to obtain high quality factor, Q, and indirectly narrow LNA bandwidth, BW, so that

$$BW = \frac{f_r}{Q} \tag{3}$$

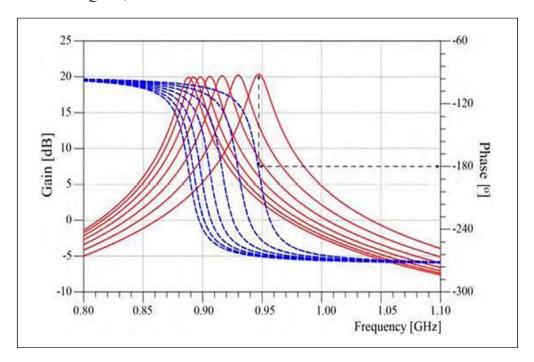

In general, when BW is narrow LNA gain is high, receiver selectivity is good, attenuation of symmetrical signals in heterodyne receiver is high, and noise level is low. LNAs' amplitude and phase characteristics are obtained by simulation. By varying the control voltage,  $V_{ctrl}$ , within a range from 1.5 up to 2.7 V the LNA resonant frequency lies in the range from 880 up to 950 MHz, and maximal gain A = 20 dB. For O = 36, BW = 25 MHz is obtained.

Figure 2. Gain magnitude and phase characteristics

According to Figure 2, and having in mind that the phase shift is defined as:

$$\theta(f_s) = -180 - \operatorname{atan}\left(2Q\frac{f_s - f_r}{f_r}\right) \tag{3}$$

maximal gain, at resonant frequency, is obtained for phase shift of -180°.

### 3. Self-tuning LNA Architecture

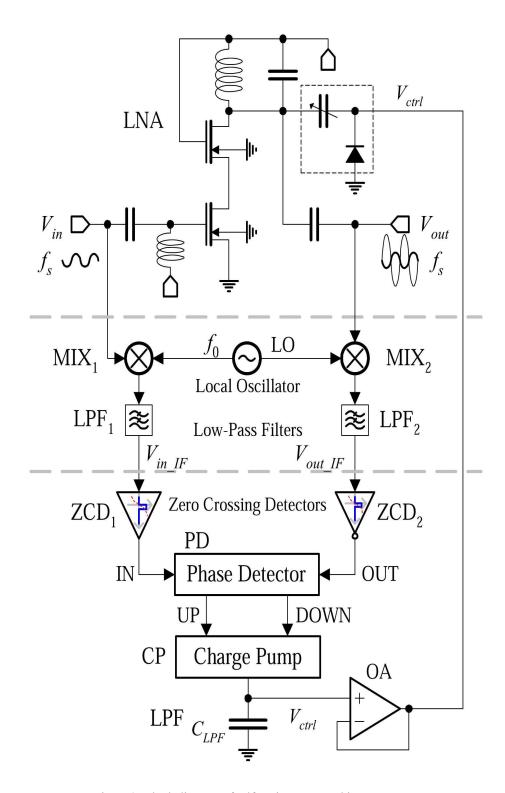

The concept of the self-tuning LNA is based on phase control strategy. The phase shift between input and output signals is used to generate control voltage,  $V_{ctrl}$ . The control voltage determines resonant frequency, i.e. indirectly the LNA phase characteristic. When the filter phase shift is  $-180^{\circ}$ , then  $f_r$  is tuned to the frequency of the input signal  $f_s$ .

The basic idea of phase control is similar to one that we meet in DLL circuits [4, 5], with one exception: Instead of pulse delay control, as it is in DLL circuits, we control the phase shift of the output signal. Block diagram of the proposed circuit is given in Figure 3. The LNA, introduced in Sec. 2, represents a building block of a self-tuning LNA architecture (see Figure 3).

Figure 3. Block diagram of self-tuning LNA architecture

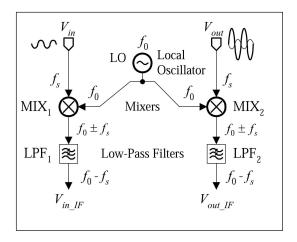

Correct operation of a phase detector is necessary to provide for accurate phase comparison. This is difficult to realize at high RF/MW frequency. Therefore frequency down conversion of signals  $V_{in}$  and  $V_{out}$  is performed by using two mixers,  $MIX_1$  and  $MIX_2$ , local oscillator, LO, as generator of frequency  $f_0$ , and two low-pass filters,  $LPF_1$  and  $LPF_2$ . This part of the circuits is given

in Figure 4. At the outputs of frequency down-converter two signals,  $V_{in\_IF}$  and  $V_{out\_IF}$ , are generated, but with lower frequency,  $f_0 - f_s$ , in respect to the frequency of RF signals,  $V_{in}$  and  $V_{out}$ .

Figure 4. Frequency down-conversion block

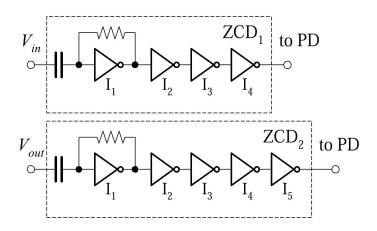

In order to estimate the phase shift between  $V_{out}$  and  $V_{in}$ , signals  $V_{out}$  and  $V_{in}$  amplified first, and after that they are shaped to rectangular forms. This is achieved by using two zero crossing detectors, ZCD1 and ZCD2.

Phase comparison of the input  $V_{in}$  and output  $V_{out}$  signals is performed by a phase detector (PD), which generates UP and DOWN signals. DOWN signal is on when the  $V_{out}$  phase leads in respect to the  $V_{in}$  phase, while in the opposite, UP signal is active. Time durations of UP and DOWN signals are proportional to the phase shift. UP and DOWN signals control the operation of a charge pump (CP). CP charges and discharges the load capacitor CLPF providing  $V_{ctrl}$  that is used as control voltage for the LNA resonant frequency. In stablestate the phase shift between  $V_{out}$  and  $V_{in}$  signals is  $-180^{\circ}$ .

Unity gain operation amplifier is used as buffer stage, primarily to decouple the influence of  $C_{LPF}$  to MVaricap capacitance, i.e. to the resonant frequency.

ZCD is implemented by a circuit presented in Figure 5. It is composed of CMOS inverter stages, denoted as  $I_1$  to  $I_5$ . The first stage,  $I_1$ , acts as a linear amplifier. Since its input is capacitive coupled with the analog signal obtained from the LNA, it eliminates the DC offset. The other stages,  $I_5$ ,  $I_4$  and  $I_5$ , operate as digital inverters.

Figure 5. Zero crossing detector

In systems with phase control loop (PLL and DLL) during stable state the phase difference between input and output signals is zero. The proposed LNA, in ideal case, involves phase shift of  $-180^{\circ}$ , therefore within the phase feedback loop is necessary to involve an additional phase shift of  $-180^{\circ}$  so that total phase shift be  $-360^{\circ}$ . The additional phase shift is obtained at the output of  $ZCD_2$ , by involving one inverter more, i.e.  $I_5$ .

More details about the structures a principles of operation of phase detector and charge pump circuits are given in [5, 7].

## 4. Simulation Results

The proposed solution, which relates to design of selftuning LNA with phase loop control, is verified by Spice simulation. The IHP design kit for  $0.25 \mu m$  SiGe BiCMOS technology was used [6]. The supply voltage  $V_{dd}$  was chosen to be 2.7 V. AC characteristics of LNA, shown in Table 1, were simulated first.

| Gain                     | 20 dB         |

|--------------------------|---------------|

| Resonant frequency range | 880 – 950 MHz |

| Bandwidth                | 25 MHz        |

| Quality factor           | 36            |

| Total noise              | 1.16 μVrms    |

| -1 dB compression point  | 72.5 mV       |

Table 1. LNA Characteristics

Figure 6. Time response of the LNA with phase control loop: (a)  $V_{out}$  (b)  $V_{in\_IF}$  and  $V_{out\_IF}$  and (c) UP, DOWN and  $V_{ctrl}$

Our design goal was to realize selective LNA whose central frequency can be tuned. During the tuning process the LNA gain and bandwidth should be keep approximately constant. The tuning process, in our design, was performed by varying the capacitance MVaricap, what was achieved by adjusting a DC biasing point. Consequently, the resonant  $f_r$  frequency was subject to change.

Figure 6 shows time responses of the self-tuning LNA with phase control loop. Settling time of the LNA output signal  $V_{out}$  is presented in Figure 6(a). The phase control loop changes the referent resonant frequency of resonant circuits until a condition  $f_r = f_s$  is fulfilled. At resonant frequency the LNA has maximal gain.

During this input signal of frequency  $f_s = 915$  MHz and local oscillator with frequency  $f_0 = 940$  MHz were used. Waveforms of the down-converted input  $V_{in\ IF}$  and output  $V_{out\ IF}$  signals that are used for driving the self-tuning LNA are presented in Figure 6(b).

UP and DOWN control signals, obtained at the outputs of PD, as well as  $V_{ctrl}$ , are given in Figure 6(c). The steady-state state is reached, i.e. the phase loop is locked, at the moment when:

- i) The signals  $V_{in}$  and  $V_{out}$  are of opposite phases,

- ii) UP and DOWN signals disappear, and

- iii) The control voltage  $V_{ctrl}$  has a constant value. The settling time of a system is approximately 900 ns.

### 5. Self-tuning LNA Application

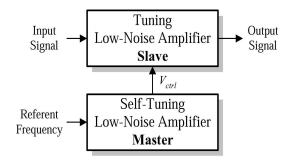

The application of LNA is given in Figure 7. The structure consists of two LNAs, master and slave. The master LNA is excited by the referent frequency source fs and it generates control voltage,  $V_{ctrl}$ . The slave LNA is of identical structure as the master. It is driven with the same control voltage  $V_{ctrl}$ , generated by the master LNA. The slave is used for amplification and filtering of the input signal.

Figure 7. Typical application for self-tuning band-pass filter

#### 6. Conclusion

In this paper we present architecture of self-tuning LNA, suitable for VLSI implementation. The central frequency is tuned by adjusting resonant frequency. The self-tuning LNA is operative in a defined frequency range (from 880 up to 950 MHz), and is characterized with relatively high quality factor Q, and high gain (20 dB), what makes this architecture suitable for realization of narrow-band amplifiers implemented in heterodyne receivers.

The phase control loop forces the filter central frequency to be equal to the input signal frequency. This is performed by changing MVaricap capacitance with control voltage, which is proportional to the integral of a phase error between filter input and output signals. The structure of a phase control loop is similar to standard phase/delay locked loop circuits [4, 5]. The proposed

architecture (900 ns) provides short overall system settling time.

The IHP 0.25  $\mu$ m SiGe BiCMOS technology was used during design and verification of the LNA. Simulation results show that the central frequency of LNA can be within the range from 880 up to 950 MHz. The LNA is designed as amplifier with 20 dB gain at central frequency, and with quality factor Q = 36. In addition, simulation results indicate that the total in-band noise is 1.16  $\mu$ Vrms and -1 dB compression point is at 72.5 mV.

## Acknowledgement

This work was supported by the Ministry of Education and Science of the Republic of Serbia, as a part of the project TR 32009.

#### References

- [1] Fatin, Gh.Z. & Kanani, Z.D.K. (2008) A very low power bandpass filter for low-IF applications. *Journal of Circuits, Systems and Computers*, 17, 685–701 [DOI: 10.1142/S0218126608004496].

- [2] Chang, Z.Y., Haspeslagh, D. & Verfaillie, J. (1997) A highly linear CMOS Gm-C bandpass filter with on-chip frequency tuning. *IEEE Journal of Solid-State Circuits*, 32, 388–397.

- [3] Changsik Yoo, Seung-Wook Lee & Wonchan Kim (1998) A±1.5-V, 4-MHz CMOS continuous-time filter with a single-integrator based tuning. *IEEE Journal of Solid-State Circuits*, 33, 18–27 [DOI: 10.1109/4.654933].

- [4] Maneatis, J.G. (1996) Low-jitter process-independent DLL and PLL based on self-biased techniques. *IEEE Journal of Solid-State Circuits*, 31, 1723–1732 [DOI: 10.1109/JSSC.1996.542317].

- [5] Stojcev, M. & Jovanovic, G. (2008) Clock aligner based on delay locked loop with double edge synchronization. *Microelectronics Reliability*, 48, 158–166 [DOI: 10.1016/j.microrel.2007.02.025].

- [6] IHP-microelectronics, SiGe: C BiCMOS technologies for MPW & prototyping, www.ihp-microelectronics.com/16.0.html.

- [7] 15, Jovanovic, G. & Mitic, D. (2013) M. Stojcev and D. Antic, Self-Tuning Biquad Band-Pass Filter, *Journal of Circuits, Systems, and Computers*, World Scientific Publishing Company, 22, 1–19.

- [8] Leroux, P., Steyaert, M. & Lna, E.S.D. (2005). Co-design for Fully Integrated CMOS Wireless Receivers. Springer: Dordrecht.