# Managing the Noise Effect of Operational Amplifiers

Georgi Valkov and Elissaveta Gadjeva Department of Electronics at Technical University of Sofia 8 Kl. Ohridski Blvd, Sofia 1000 Bulgaria gvalkov@abv.bg egadjeva@tu-sofia.bg

**ABSTRACT:** In the low noise operational amplifiers, the noise is an issue. To offset the noise effects, we have developed a description Verilog which is a dynamic macro-model. We have also performed testing and found that the model is more efficient when comparing with the compatible Spice library model.

Keywords: Effectiveness, Verilog-A, Noise Macromodel, Current Feedback Operational Amplifier

Received: 27 May 2022, Revised 19 August 2022, Accepted 30 August 2022

**DOI:** 10.6025/jes/2022/12/4/105-110

Copyright: with Authors

### 1. Introduction

The high-level Analog Hardware Description Language (AHDL) Verilog-A describes the structure and behavior of analog systems and their components using modules. Verilog-A combines structural modeling with language based behavioral modeling. An important feature of the language is that it includes coupled algebraic-integro-differential equations, rich set of analog operators, if-then and case statements, as well as implicit and explicit equations [1]. Methodologies and uses of analog behavioral modeling with the Verilog-A language are developed in [2]. Simplified Verilog-A models of operational amplifiers are proposed in [2-4]. A number of research academic and industrial groups create compact models using Verilog-A, which are used to simulate electronic devices and circuits correctly and efficiently. In [5] recommendations are provided for writing and optimization of the compact models in Verilog-A. As a result, the language Verilog-A can be characterized as an extremely efficient language for writing compact models. Recently, the AHDLs are widely used in the areas of analog and RF circuit simulation. The capabilities and limitations of compact models of analog RF circuits are discussed in [6]. Correlated noise models are developed in [7] using Verilog-A language. They are used in the simulation of the noise behavior of MOSFET using correlated noise sources with complex correlation coefficients.

There are many opamp macromodels described in the Verilog-A and VHDL-AMS languages [2-4], but most of them are too

simplified. In addition to that, the noise behavior of the actual devices, which is very important for models of high precision low-noise opamps, is not considered by those models [2-6].

In the present paper a detailed macromodel is developed for the LM6181 current feedback operational amplifier, using the Verilog-A language. The model includes noise effects. The model efficiency is investigated and compared to the corresponding PSpice library model.

### 2. Noise Modelling of the Operational Amplifiers

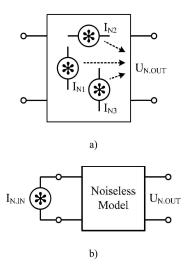

When modeling noisy two-port devices (Figure 1a), such as operational amplifiers, the output noise is referred to the input port of the device. As a result, a noiseless model is created, and finally a noise block is added to the input (Figure 1b).

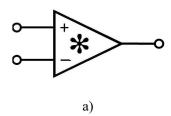

For a noisy operational amplifier (Figure 2a), the noise block consists of two current noise sources  $I_{N1}$  and  $I_{N1}$ , connected between the corresponding input and the reference node, and a voltage noise source in series with one of the inputs, as shown in Figure 2b. The signals from these noise sources are frequency dependent and can be obtained from the datasheet of the opamp.

Figure 1. Two-port device with noise (a) and equivalent representation as a noiseless model and referred noise to the input (b)

## 3. Noise Implementation in the Spice Model

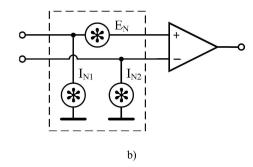

The noise sources  $I_{N1}$ ,  $I_{N2}$  and  $E_N$  (Figure 2b) are realized in the computer realization of the *Spice* macromodel [12] using auxiliary circuits shown in Figure 3, that create the noise signals for the corresponding noise sources.

The resistor  $R_{32}$  creates the white noise current for  $I_{N2}$ . The resistor  $R_{33}$  creates the white noise current for  $I_{N1}$ . The voltage between nodes  $n_{59}$  and  $n_{61}$  defines EN. It includes flicker and shot noise from the diodes  $D_9$  and  $D_{10}$ , as well as white noise from the resistors  $R_{30}$  and  $R_{31}$ .

Figure 2. Symbol of a noisy op-amp (a) and equivalent representation as a noise block added to the inputs of a noiseless op-amp model (b)

The symmetric implementation cancels out the  $D_C$  component from  $V_{15}$  and  $V_{16}$ , which are used to set the required operating point of the two diodes. Taking into account that the Modified Nodal Approach (MNA) is applied in the circuit simulators, the auxiliary circuit in Figure 3 increases the matrix order of the op-amp model by  $10-\sin$  additional nodes ( $n_{58}$ ,  $n_{59}$ ,  $n_{60}$ ,  $n_{61}$ ,  $n_{62}$  and  $n_{63}$ ) and four additional equations describing the independent voltage sources  $V_{15}$ ,  $V_{16}$ ,  $V_{17}$  and  $V_{18}$ .

Figure 3. Noise signals

# 4. Noise Modelling in Verilog-A

In Verilog-A the noise is implemented using the white\_noise, flicker\_noise, and noise\_table functions [10]. The parameter of the white\_noise function specifies the noise level. The first parameter of the flicker\_noise function is the noise level at 1Hz. The second parameter is the frequency exponent. The parameter passed to the noise\_table function defines the noise levels for a number of frequency points, using the following form:  $\{f_1, v_1, f_2, v_2, \dots, f_n, v_2\}$ . For some simulators, a file name can be specified as the parameter for noise\_table. Each line of the file should contain a pair of frequency point and noise level. All noise levels described above are in  $V^2/Hz$ . A sample block of noise voltage source has the following form:

An advantage of Verilog-A is that the noise functions can be integrated as a part of the model equations. No auxiliary circuits are needed and the matrix order is not affected.

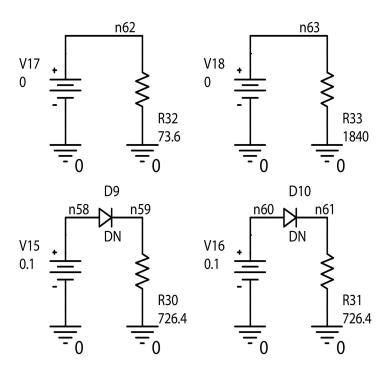

The Verilog-A implementation of LM6181 current feedback op-amp macromodel with noise is shown in Figure 4.

#### 5. Effectiveness Assessment

The noise models based on behavioral modeling using Verilog-A are characterized with higher efficiency, due to the fact that they do not increase the order of the circuit matrix. The auxiliary block that generates the noise signals, shown in Fig. 3, which are required by the Spice macromodel, increases the model matrix order n by 10 and reduces the efficiency of the model.

The relative speed increasing using the Verilog-A model, compared to the Spice model has the form:

$$\varepsilon_C = 100 \, \frac{t_S - t_V}{t_S} \, [\%], \tag{1}$$

where  $t_S$  is the simulation time, when using the library Spice model for LM6181 and  $t_V$  is the simulation time for the Verilog-A model from Figure 4.

The dependence of  $\varepsilon_C$  on the matrix order n is shown in Figure 5. The model accuracy of the Verilog-A implementation is the same as for the Spice model.

In order to assess the effectiveness of the two models depending on the matrix order, the following circuits are simulated: a single non-inverting amplifier with a matrix order n=71 for the Spice model; a circuit with three amplifiers (n=199); a circuit with five amplifiers (n=327) and a circuit with seven amplifiers (n=455).

The following simulation settings are used: AC interval [1Hz-1GHz], 10k points/decade, and Print interval for noise contribution table: every 5th point. All circuits are simulated in the environment of Dolphin SMASH [11].

The time measurements are performed by a custom plugin, which hooks the simulation start and end events, and reports the time difference. The plugin uses the RDTSC processor instruction and enables time measurements to be performed with a very-high precision. In addition to that, exclusive mode is enabled in the simulator, the process and thread priorities are set to real-time, and the affinities are locked to a single CPU core. This results in a very low maximum deviation time, less than 0.8% from the mean value. To further enhance the precision, 12 simulations are run in each case and the best 8 times are averaged to calculate the mean time.

```

// LM6181 current feedback Op-Amp macromodel with

I(GI1) <+ 243.75u + V(in) *2.708u;

I(GI2) <+ 243.75u + V(in) *2.708u;

noise

// in+ in- v+ v- out

I(FI2) <+ I(va4)*100; I(GR1) <+ V(GR1)*238u;

module LM6181 ns(n01, n02, n99, n50, n41);

I(C1) <+ ddt(V(C1))*468f; I(GR2) <+ V(GR2)*238u;

inout n01, n02, n99, n50, n41;

I(C2) <+ ddt(V(C2))*468f; I(GR3) <+ V(GR3)*1.58m;

electrical n01, n02, n99, n50, n41;

V(V1) <+ 0.3; I(RE1) <+ V(RE1)/130;

electrical n03, n04, n05, n06, n07, n08, n09;

I(GR4) <+ V(GR4)*1.58m; I(FI1) <+ I(va3)*100;

electrical n10, n11, n12, n13, n15, n16, n17;

V(V2) <+ 0.3; I(RE2) <+ V(RE2)/150

electrical n20, n21, n22, n23;

V(va3) <+ 0; V(va4) <+ 0;

electrical n30, n31, n33, n34, n35, n36, n37, n38;

I(GR6) <+ V(GR6)*50n; I(GR7) <+ V(GR7)*50n;

electrical n40, n44, n45, n46, n47, n49;

I(GB1) <+ -1.2u + V(in)*40n + V(n56 qnd)*1m;

electrical n55, n56, n57, n98, gnd; ground gnd;

I(FN1) \leftarrow \text{white noise}((3.00143e-12)*(3.00143e-12));

branch(n99, n05) GI1, FI1; branch(n04, n50) GI2,

I(CIN1) <+ ddt(V(CIN1))*2p;</pre>

I(GB2) <+ 18.5u-V(in)*150n-V(n01_n49)*100n-

V(n55__gnd)*1u;

branch(n05, n06) GR1; branch(n06, n99) C1;

branch(n04, n07) GR2; branch(n07, n50) C2;

I(FN2) <+ white_noise((1.50071e-11)*(1.50071e-11));</pre>

branch(n99, n08) GR3; branch(n99, n10) V1;

I(CIN2) <+ ddt(V(CIN2))*5.75p;</pre>

branch(n10, n30) RE1; branch(n50, n09) GR4;

V(EOS) < + -2.8m + V(in)*93u + V(n45 gnd) + V(n47 gnd)

branch(n11, n50) V2; branch(n11, n31) RE2;

+V(n57 gnd) + flicker noise((2.86835e-8)*(2.86835e-

branch(n12, n05) va3; branch(n04, n13) va4;

8), 1)

branch(n01, n99) GR6, GB1; branch(n01, n50) GR7;

+ white noise ((3.97682e-13) * (3.97682e-13)

branch(n01, gnd) FN1, CIN1; branch(n99, n02) GB2;

/* second stage */ + (4.90727e-9)*(4.90727e-9));

branch(n02, gnd) FN2, CIN2; branch(n03, n01) EOS;

I(I3) <+ 4.47m; V(EH) <+ V(R8);

branch(n99, n50) in; branch(n56, gnd) n56__gnd;

I(R8) \leftarrow V(R8)/7.19k; V(V3) \leftarrow 1.7;

branch (n01, n49) n01 n49; branch (n55, gnd)

I(R9) <+ V(R9)/7.19k; V(V4) <+ 2;

I(G1) <+ V(GR3)*1.58m + V(GR4)*1.58m;

n55 gnd;

branch(n45, gnd) n45__gnd; branch(n47, gnd)

// Fp1 = 27.96 KHz

n47 gnd;

I(R5) \leftarrow V(R5)/2.372e+6; I(C3) \leftarrow ddt(V(C3))*2.4p;

branch(n57, gnd) n57__gnd;

I(G2) \leftarrow V(n15_n49) \times 1m; // pole stage, Fp = 250 MHz

branch(n99, n50) I3; branch(n99, n49) R8;

I(R14) \leftarrow V(R14)/1k; I(C4) \leftarrow ddt(V(C4))*692f;

I(G3) <+ V(n20_n49)*1m; // pole stage, Fp = 250 MHz

branch(n49, n50) R9; branch(n99, n16) V3;

branch(n17, n50) V4; branch(n99, n98) EH;

I(R15) \leftarrow V(R15)/1k; I(C5) \leftarrow ddt(V(C5))*692f;

I(G4) \leftarrow V(n21_n49) \times 1m; // pole stage, Fp = 275 MHz

branch(n98, n15) G1, R5, C3;

I(R16) \leftarrow V(R16)/1k; I(C6) \leftarrow ddt(V(C6))*578.7f;

branch(n98, n20) G2, R14, C4; branch(n15, n49)

I(G5) \leftarrow V(n22_n49)*1m; // pole stage, Fp = 500 MHz

n15_n49;

I(R17) \leftarrow V(R17)/1k; I(C7) \leftarrow ddt(V(C7))*318.3f;

branch (n98, n21) G3, R15, C5; branch (n20, n49)

n20_n49;

// PSRR stage

I(G10) <+ V(n99\_gnd)*141.3u;

branch(n98, n22) G4, R16, C6; branch(n21, n49)

n21 n49;

V(L3) \leftarrow ddt(I(L3)) \times 26.53u; I(R25) \leftarrow V(R25)/10;

branch(n98, n23) G5, R17, C7; branch(n22, n49)

I(G11) <+ V(n50 gnd)*141.3u;

V(L4) <+ ddt(I(L4))*2.27364u; I(R26) <+ V(R26)/10;

n22 n49;

branch(gnd, n45) G10; branch(n44, n45) L3;

// thermal effects

branch(n44, gnd) R25; branch(gnd, n47) G11;

I(I12) \leftarrow 1; I(R27) \leftarrow V(R27) / (10*Tc(3.453m, 79.3u));

branch(n46, n47) L4; branch(n46, gnd) R26;

I(I13) \leftarrow 1m; I(R28) \leftarrow V(R28)/(1.5*Tc(930.3u)

branch(n99, gnd) n99 gnd; branch(n50, gnd)

80.75u));

n50 gnd;

I(I14) \leftarrow 1m; I(R29) \leftarrow V(R29) / (3.34*Tc(3.111m, 0));

branch (gnd, n55) I12, R27; branch (gnd, n56) I13,

// output stage

R28;

I(F6) <+ I(va7); V(va7) <+ 0;

branch(gnd, n57) I14, R29;

I(F5) <+ I(va8); V(va8) <+ 0;

branch(n99, n50) F6; branch(n99, n35) F5;

V(E1) \leftarrow V(n99 \quad n23); V(V5) \leftarrow 5.3;

branch(n99, n36) va7; branch(n99, n37) E1;

I(R35) <+ V(R35)/50; V(V6) <+ 5.3;

branch(n37, n38) va8; branch(n38, n40) R35;

I(CF1) <+ ddt(V(CF1))*2.1p; V(L5) <+ ddt(I(L5))*31n;

branch(n33, n40) V5; branch(n40, n34) V6;

I(RL5) <+ V(RL5)/100k;

branch(n41, n02) CF1; branch(n40, n41) L5, RL5;

end

branch(n99, n23) n99 n23;

// input stage

// temperature coeffitient scaling factor

QPN Q1 (n50, n03, n05); DX D1 (n30, n08);

parameter real Tnom=$simparam("tnom")+273.15 from

QNN Q2 (n99, n03, n04); DX D2 (n09, n31);

QNI Q3 (n08, n06, n02); DY DS1 (n03, n12);

(0:inf);

analog function real Tc;

QPI Q4 (n09, n07, n02); DY DS2 (n13, n03);

input TC1, TC2; real TC1, TC2; begin

// second stage

Tc = 1 + ($temperature-Tnom) * (TC1+($temperature-

DX D3 (n15, n16); DX D4 (n17, n15);

Tnom) *TC2);

// output stage

DX D7 (n36, n35); DX D8 (n35, n99);

end endfunction

// input stage

DX D5 (n23, n33); DX D6 (n34, n23);

analog begin

endmodule

```

Figure 4. Verilog-A implementation of LM6181 current feedback op-amp macromodel with noise

### Acknowledgement

The investigations are supported by the project ?122PD0026-03.

#### 6. Conclusion

A detailed computer macromodel of the current feedback operational amplifier has been developed using the Verilog-A language. The model includes noise effects. The model accuracy of the Verilog-A implementation is the same as for the Spice model. The corresponding code is given. The model efficiency is investigated and compared to the corresponding Spice library model.

### References

- [1] Miller, I. & Cassagnes, T. Verilog-AMS Eases Mixed Mode Signal Simulation, technical. Proceedings of the 2000 International Conference on Modeling and Simulation of Microsystems, pp. 305–308.

- [2] FitzPatrick, D. & Miller, I. (2003). Analog Behavioral Modeling with the Verilog-A Language. Kluwer Academic Publishers.

- [3] www.eda.org/twiki/bin/view.cgi/VerilogAMS.

- [4] w2.cadence.com/appnotes/CDN\_Creating Analog Behavioral Models.pdf.

- [5] Frevert, R. et al. (2005). Modeling and Simulation for RF System Design. Springer: Berlin, ISBN-100-387-27585-1, pp. 219-246.

- [6] Qin, Huabiao & Wang, F. (2006). Modeling of Operational Amplifier Based on VHDL-AMS. IEEE Publications, pp. 894-897.

- [7] Coram, G.J. (2004) How to (and how not to) write a compact model in Verilog-A. *Proceedings of the IEEE International Behavioral Modeling and Simulation Conference (BMAS 2004)*, pp. 97–106.

- [8] Troyanovsky, B., O'Halloran, P., Mierzwinski, M. (2005), Digest of Papers "Analog RF model development with Verilog-A", Radio Frequency integrated Circuits. Symposium. *IEEE Publications*, 12-14 June 2005, 2005, 287–290.

- [9] McAndrew, C., Coram, G., Blaum, A. & Pilloud, O. (2005) Correlated noise modeling and simulation. *In: Proceedings of the Tech. Workshop Compact Modeling*, Anaheim, CA, pp. 40–45.

- [10] Verilog-AMS Language Reference Manual, version 2.3.1, Accellera (2009).

- [11] Dolphin Integration SMASH overview. www.dolphin.fr/medal/smash/smash overview.php.

- [12] "Development of an Extensive SPICE Macromodel for Current- Feedback Amplifiers", Texas Instruments, May (2004). www.ti.com/lit/an/snoa247a/snoa247a.pdf.