# A novel Topology of Delta Modulation Technique for Improving the Power Factor of AC-DC Converters

Walid Emar Al-Isra Private University Amman, Jordan Walidemar23@yahoo.com

**ABSTRACT:** This work presents a new topology of delta modulation technique. This kind of modulation technique is usually used to improve the power factor of Pulse Width Modulation (PWM) converters used for supplying A.C. drives. Many new topologies have been presented trying to obtain a cost-effective solution to reduce the input current harmonic content and to make it sinusoidal and in phase with the input voltage of AC-DC converters. Each one of them has its application range due to the inherent characteristics of the topology (See [2]). Obviously, not every converter is useful for the same application. Hence, this paper tries to show the most appropriate topology of different variants of modulation technique used for power factor correction. This technique which is used to generate the PWM control signals for the main devices of the PWM converter has the advantage of yielding instantaneous current control, resulting in a fast response [3], [4]. However, the switching frequency is not constant and varies over a wide range during each half-cycle of the A.C. input voltage. Furthermore, the frequency is also sensitive to the values of the circuit components, which is also addressed in this paper. This new delta modulation technique topology proves to give great stability performance over other variants of delta modulation or other modulation techniques.

Keywords: AC-DC Converter, Delta Modulation Technique (DMT), New Topology, Power Factor (PF), Simulation and Modulation.

Received: 1 July 2009, Revised 19 August 2009, Accepted 24 August 2009

### 1. Introduction

It is well known that the input voltage and current waveforms of ideal AC-DC converters are sinusoidal and in phase. However, the current waveforms of practical AC-DC converters are non-sinusoidal and contain certain harmonics. As a result of that, the phase shift between the input current fundamental component and the voltage of AC-DC converter is increased. The power factor (**PF**) which depends on the delay angle of AC-DC converter, the phase shift between the input current and voltage and the circuit component are then reduced [8]. With the aid of modern control technique and the availability of high speed semiconductor devices, the input current can be made sinusoidal and in phase with the input voltage, thereby having an input power factor of approximate unity.

Delta modulation, also known as ripple controller control, maintains the AC-DC converter input current within a defined window above and below a reference sine wave. The greatest benefits of delta control are that it offers fast load transient response and eliminates the need for feedback-loop compensation. The other well-known characteristic is the varying operating frequency.

However, the regulation inaccuracy issue of the delta controlled converter is almost unknown to engineers. Until now, research on delta controllers has mainly focused on transient analysis and transient modeling [1-3]. The first analysis of accuracy was performed on a current mode delta controller specifically designed to power microprocessors [5]. However, the regulation accuracy of the more widely used current-mode delta-controlled controllers is still unknown.

Furthermore, bang-bang technique used in [2] for the same purpose as DMT suffers from certain drawbacks. For example, it does not enable a simple realization of the shifted switching of the bridge converters that are connected in parallel. The shifted switching evidently reduces the ripple of the current derived from the trolley. It also requires a very fast microprocessor since it needs a very short current sampling period.

In this paper a new topology with new algorithms for generating the PWM control signals for the transistors of the converter is introduced to delta modulation technique (**DMT**). These new algorithms are solved by using high frequency semiconductor

devices and suitable control circuitries. The result of using such algorithms is not only improved performance of the converter, and optimal waveform of the current derived from the trolley, but also the shifted switching of the parallel connected converters will be no longer needed [3], [7].

The remainder of the paper is organized as follows: Section II presents the principle of operation and an overview of the algorithms used for switching the transistors of the converter. Different logic algorithms and some simulation obtained as a result of using these algorithms for delta modulation is shown in Section III. Finally, Section IV gives the conclusions to the paper.

## 2. Principle of operation of DMT

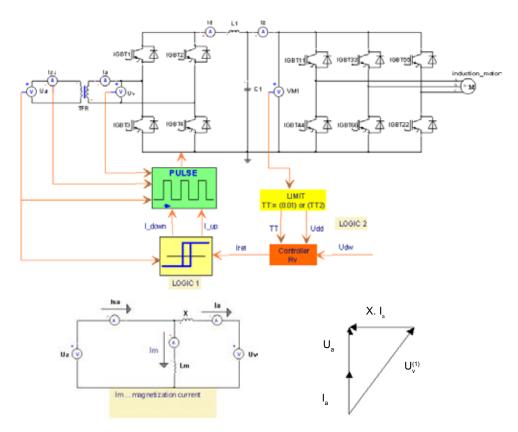

Figure 1 shows a unity PF circuit that combines a full bridge AC-DC converter and a full bridge voltage inverter (frequency converter). The control circuits of AC-DC converter have two main functions:

- Ensuring a unity PF (sinusoidal current which is in phase with the input voltage).

- Ensuring a constant voltage  $U_d$  across the capacitor

The first function 1 can be easily realized, as the boundary values of the hysteresis band  $I_{w^2}$  and  $I_{w^1}$  are generated such that the 1<sup>st</sup> harmonic component of the current derived from the trolley is in phase with the voltage, as will be shown later in the paper. The switching transistors change their state as soon as current  $I_{w^2}$  reaches the reference boundary value of the hysteresis band.

The second function is obtained by using a voltage controller  $R_v$  of voltage  $U_d$  which generates a suitable value for the reference current  $I_{ref}$  that is derived from the trolley (during motoring regime  $I_{ref}>0$ , and during braking regime  $I_{ref}<0$ ). From the simulation obtained in the next sections it is clearly evident that there is a certain relationship between the amplitude of current Ia, current Id, current I<sub>c</sub> and consequently with voltage  $U_d$  at the output.

The voltage controller  $R_v$  regulates the mean value of voltage  $U_d$  which is always estimated at the instant of sampling of  $R_v$ . With respect to the required current waveform it is good to have  $I_w$  constant during each halve cycle of the required current.

This delta method of control keeps the input current I<sub>sa</sub> within the window hysteresis band around the reference current I<sub>ref</sub>

Figure 1. Frequency converter circuit arrangement for unity PF

which leads the sinusoidal value of this current I<sub>a</sub> to be in phase with the sinusoidal voltage U<sub>a</sub> and without any dc offset. To obtain a sinusoidal current the sampling of the controller must be synchronized with the current waveform and the sampling period must be TT = 0.01. A new value of I<sub>ref</sub> must be estimated exactly at the zero-crossing of current I<sub>a</sub>.

f = 100 HZ. This component increases the ripple of current I<sub>d</sub> and voltage U<sub>d</sub>.

When the controller sampling period is TT = 0.01S, then the output of the controller under steady state conditions I<sub>ref</sub> is purely constant. The sampling period TT of R, may cause a time delay in the voltage control circuit. Therefore, it is necessary to reduce TT during transients. This therefore will result in a staircase waveform of the current but the dynamic properties of the voltage control loop are improved substantially.

Figure (1) shows clearly how the voltage and current derived from the trolley are measured. It is therefore evident that voltage U<sub>a</sub> must be measured at the primary side of the transformer. The current on the other hand, may be measured at the secondary side since current I<sub>a</sub> may be obtained as the average value of current I<sub>a</sub>.

### 3. Logic 1 used for switching of main transistors

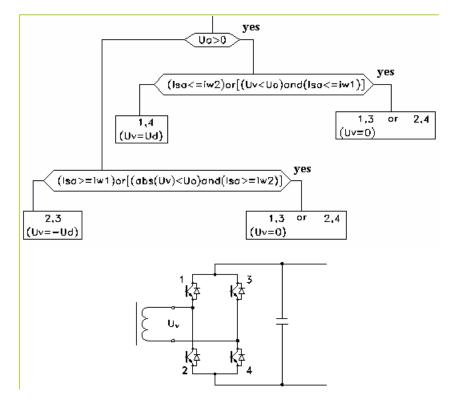

Logic1 demonstrates the algorithms used in delta modulation for generating PWM gating signals for the main transistors of AC-DC converter. The switch state of AC-DC converter is in general determined by comparing  $U_{v}$  with  $U_{0}$ , where  $U_{0}$  is an arbitrary voltage determined as follows:  $0 < U_0 < (U_d)_{min}$ . Around the zero-crossing of voltage  $U_a$ , voltages  $+U_d$ ,  $-U_d$  are applied alternatively at the ac input terminals of AC-DC converter.

#### 3.1 First variant of Logic 1

Figure 2a. Variant 1 of Logic 1

- $I_{sa} < i_{down} \dots U_v = 0$   $I_{sa} > i_{up} \dots U_v = U_d$

- $i_{_{_{_{_{sa}}}} < I_{_{sa}} < i_{_{_{up}}} \dots$  hysteresis effect

- $\overline{U}_0^{\text{norm}}$  arbitrary voltage ( $0 < U_0 < U_{d(\min)}$ ), the switching state of the converter is determined by comparing  $U_v$  with  $U_0$ .

$\Delta I = 60A, U_a = 70\% of U_{an}$

Figure 2b. Simulation results of variant 1

• Note: Concerning this variant of Logic 1, as it is seen of the above simulation, current I<sub>a</sub> leaves the window limits around the zero-crossing of U<sub>a</sub> which adds a certain drawback to this variant. Current I<sub>a</sub> also increases very slowly when U<sub>a</sub> is so small.

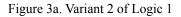

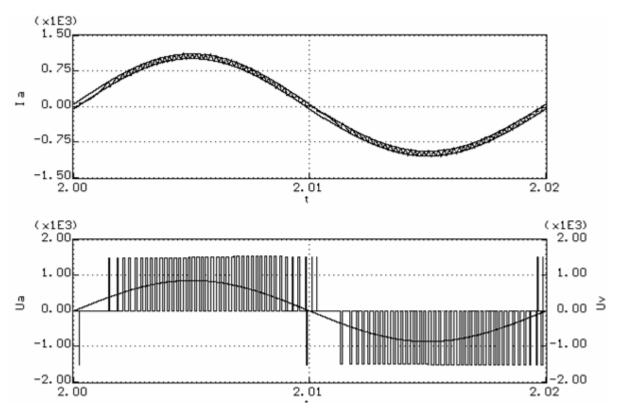

## 3.2 Second variant of Logic 1

To force current  $I_a$  to stay within the given hysteresis window limits  $I_{w1}$ ,  $I_{w2}$ , then in accordance with the required current, voltage  $U_d$  must be applied instead of a zero voltage across the a.c. terminals of the converter. The algorithm with the results obtained is shown in the following figures:

dI<sub>w</sub> ... tolerance current ripple

$U_0 \dots$  arbitrary voltage (  $0 < U_0 < (U_d)_{\min}$ ) (comparing U<sub>v</sub> with U<sub>0</sub> determines the switching state of the converter)

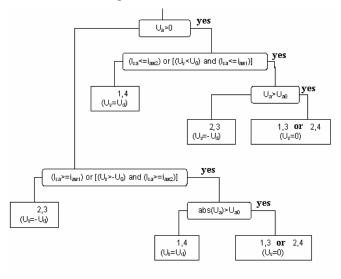

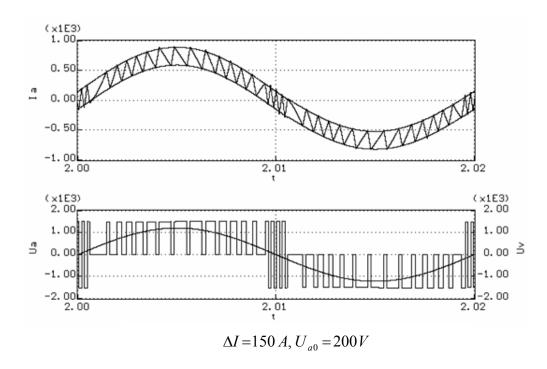

Figure 3b. simulation results of variant 2

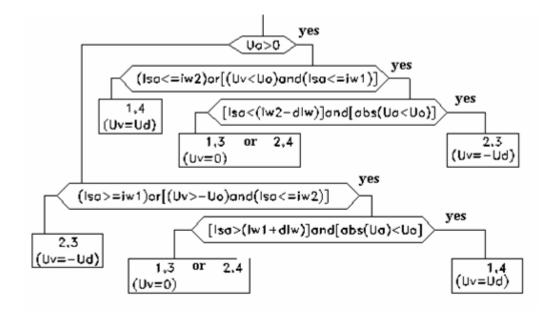

#### 3.3 Third variant of Logic 1

To improve the voltage waveform around zero-crossing shown in figure 2b, voltages  $+U_d$  and  $-U_d$  are applied alternatively at the a.c. terminals of the converters. Variant 3 of Logic 1 and the results obtained are shown in the following figure:

$U_0 \dots$  arbitrary voltage, (  $0 < U_0 < (U_d)_{\min}$ ) and again comparing  $U_v$  with  $U_0$  determines the switching state of the converter.

If  $U_a < U_{a0}$  , then the function of Logic 1 is changed.

Figure 4a. Variant 3 of Logic 1

The simulation results of this variant are shown in the following figure:

Figure 4b. Simulation results of variant 3

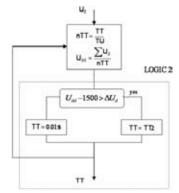

#### 4. Logic 2 for determining the sampling period TT of controller R

Logic 2 in Figure (5) explains the algorithm used to test the sampling period TT of  $R_v$ . The operating period of the voltage controller  $R_v$  is divided into samples. If the deviation between the mean value of the voltage across the capacitor  $U_{dd}$  during the sampling period TT and the given dc reference is greater than  $\Delta Ud$ , a shorter period TT2 is then applied. In our simulation example we consider the dc reference voltage to be 1500V. Using this technique, the output voltage  $U_d$  is always forced to remain within a fixed given value, and this exactly what is needed.

- TT is the sampling period of  $R_y$ .

- TU is the sampling period of voltage U<sub>d</sub>

- $U_{dd}$  is the mean value of voltage  $U_d$  over period TT

Figure 5a. Logic 2 used for testing TT of Rv

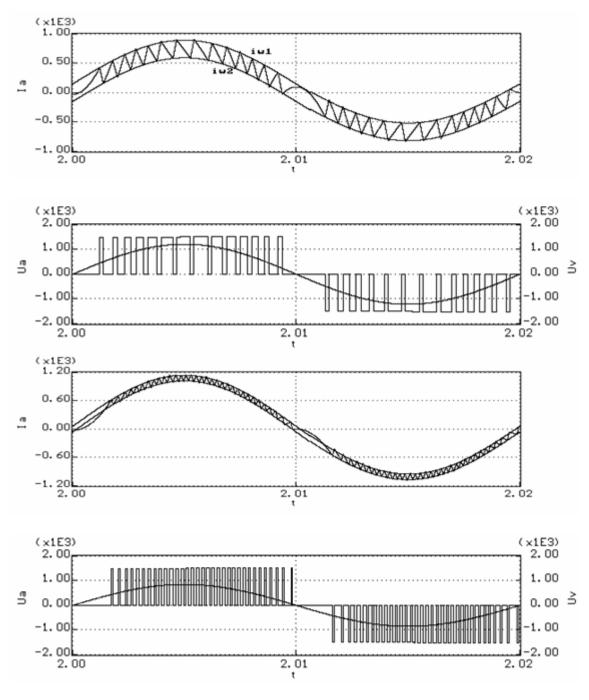

#### 5. Variant 3 of Logic 1 - Best simulation results

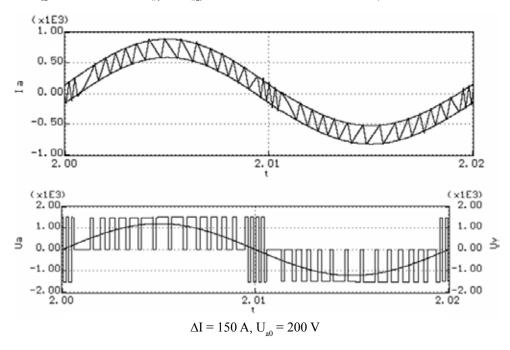

A demonstration of delta modulation using the above mentioned algorithms is prepared using Matlab 6.5 and software programming language "Pascal". Such work was carried out under the condition of negligible magnetization current. This current is shifted by 90° with respect to voltage  $U_a$  because of the prevailing leakage flux at the secondary side of the transformer. The current  $I_a$  is forced to remain between the upper and the lower limit of reference window band. To achieve this result, the primary current  $I_{sa}$  is compared with  $I_{w1}$  and  $I_{w2}$  For the same purpose voltage  $U_v$  is compared with an arbitrary voltage

Figure 5b. Input voltage and current waveforms

$U_0$  whose value must be greater than zero and smaller than the minimum value of  $U_d$  (as depicted in figure 3). The results of using different algorithm variants for implementing delta modulation technique is current  $I_a$  and voltage  $U_a$  as it is shown in figures 2, 3, 4. The fundamental components are in phase and therefore, by deploying this means of control, the target of improving the power factor of AC-DC converter is achieved. However, variants 3 gives better results than variant 1 and 2 as it is shown in figure 5, 6 and 7.

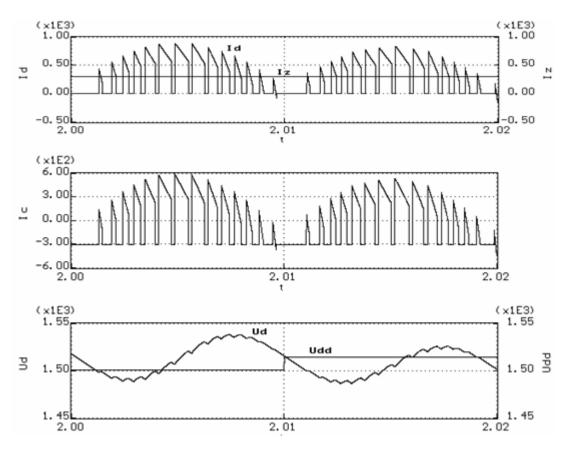

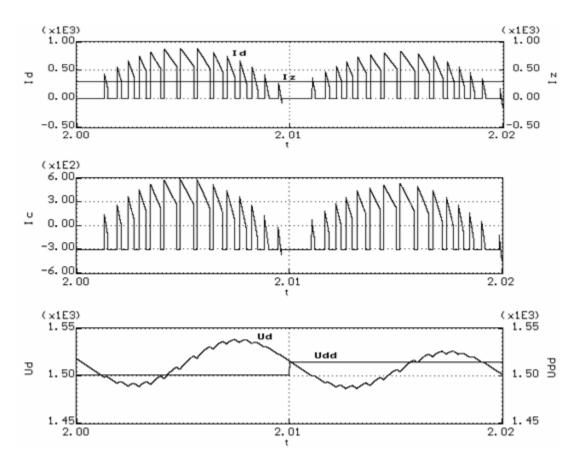

Figures (5, 6 & 7) below are graphical representations of variant 3 - Logic 1 and Logic 2. These figures are obtained under the conditions of disconnected and connected filter at the output. The aim of logic 2 is to obtain a constant voltage at the output of AC-DC converter and the input of the voltage inverter.

Figure 6. Output voltage waveforms obtained for a disconnected output filter L1, C1

- TT = 0.01s, T1 = 1/50000s,  $\Delta I = 150 A$

- measuring period of voltage  $U_d$  is TU = 1/1000 s

- Operating period of voltage regulator  $R_v$  is variable

- Transformer secondary voltage  $U_{an} = 860 V$

- No min al sec ondary current  $I_{an} = 663 A$

- Short circuit volatge of a transformer  $e_k = 30\%$

Figure 7. Output voltage waveforms obtained with a connected output filter L1, C1, filter  $C_1 = 8 \text{ mF}$ ,  $L_1 = 0.316 \text{ mH}$

- TT = 0.01s, T1 = 1/50000s,  $\Delta I = 150 A$

- measuring period of voltage  $U_d$  is TU = 1/1000 s

- Operating period of voltage regulator  $R_v$  is variable

- Transformer sec ondary voltage  $U_{an} = 860V$

- No min al sec ondary current  $I_{an} = 663 A$

- Short circuit voltage of a transformer  $e_k = 30\%$

#### 6. Conclusion

It can be concluded that, by controlling the input current of a bridge AC-DC converter with the aid of a suitable control technique, the input current of AC-DC converter can be made sinusoidal and in phase with the input voltage, thereby having an input PF of approximate unity, resulting of a more stable performance of the system. The reference dc voltage value for  $U_{dd}$  was considered to be 1500-V.

Concerning the filter used at the output of AC-DC converter to filter out the high harmonics generated there it may badly affect the dynamic properties of the motor. The simulation however shows that the parameters considered as optimal for the motor without a filter are suitable even for a motor with a filter.

On the other hand the converter can be combined with a high frequency single phase buck-boost converter to reduce the size of the filter. This combination will allow the use of the filter, reduce its bad effect on the motor and make the power factor at the input of the converter more closed to unity.

### **List Of Abreviations**

#### References

- A.Fernandez, J. Sebastian, M.M. Hernando, P. Villegas, J. Garcia, "Helpful hints to select a power-factor-correction solution for low- and medium-power single-phase power supplies," *IEEE Trans. on Industrial Electronics*, vol. 52, no. 1, pp. 46- 55, Feb 2005.

- [2] P. D. Ziogas, L. Morán, G. Joos, and D. Vincenti, "A refined PWM scheme for voltage and current source converters", IEEE-IAS Annual Meeting, 1990, P. 997-983.

- [3] R. Wu, S. B. Dewan, and G. R. Slemon, "Analysis of an AC-to-DC voltage source converter using PWM with phase and amplitude control", IEEE Transactions on industry Applications, vol. 27, No. 2, March/April 1991, pp. 355-364.

- [4] X. Ruan, L. Zhou, and Y. Yan, Soft-switching PWM three-level converters," IEEE Transactions on Power Electronics, Vol. 6, No. 5, September 2001, p. 612-622.

- [5] M. H. Rashid, Power Electronics, Circuits, Devices and applications, Third edition, 2004, Pearson Education, Prentice Hall, Upper Saddle River, NJ 07458.

- [6] Miftakhutdinov, R. "An Analytical Comparison of Alternative Control Techniques for Powering Next Generation Microprocessors," TI Seminar, 2002.

- [7] G. Moschopoulos, P. Jain, Single-phase single-stage power-factor-corrected converter topologies," *IEEE Trans. on Industrial Electronics*, vol. 52, no. 1, p. 23- 35, Feb 2005.

- [8] J.-C. Crebier, B. Revol, J.P. Ferrieux, Boost-chopper-derived PFC rectifiers: interest and reality," *IEEE Trans. on Industrial Electronics*, vol. 52, no. 1, p. 36-45, Feb 2005.

- [9] F.J. Azcondo, C. Branas, R. Casanueva, S. Bracho, Power-mode-controlled power-factor corrector for electronic ballast," *IEEE Trans. on Industrial Electronics*, vol. 52, no. 1, pp. 56-65, Feb 2005.

- [10] E. Figueres, J.-M. Benavent, G. Garcera, M. Pascual, "Robust control of power-factor-correction rectifiers with fast dynamic response," *IEEE Trans. on Industrial Electronics*, vol. 52, no. 1, p. 66-76, Feb 2005.

- [11] J. W. Dixon, and B.-T. Ooi, "Indirect current control of a unity power factor sinusoidal current boost type three-phase rectifier," IEEE Transactions on Industrial Electronics, Vol. 35, No. 4, November 1988, p. 508-515.

- [12] P. D. Ziogas, "Optimum voltage and harmonic control PWM techniques for 3-phase static UPS systems," IEEE Transactions on industry Applications, Vol. IA-16, No. 4, 1980, p. 542-546

- [13] Miftakhutdinov, R. "An Analytical Comparison of Alternative Control Techniques for Powering Next Generation Microprocessors," TI Seminar, 2002.

- [14] Song, C., and Nilles, J. "Accuracy Analysis of Hysteretic Current-Mode Voltage Controller," Proc. IEEE APEC, 2005, pp. 276-280.

- [15] H. Inose, Y. Yasuda and J. Marakami, "A telemetering system by code modulation, delta-sigma modulation," IRE Trans. on Space, Electronics and Telemetry, SET-8, p. 204-209, Sept. 1962.

- [16] H. Nyquist, "Certain topics in telegraph transmission theory," AIEE Trans., p. 617-644, 1928.

- [17] M. Armstrong, et al, "A COMS programmable self-calibrating 13b eight-channel analog interface processor," ISSCC Dig. Tech. Paper, p. 44-45, Feb. 1987.

- [18] K. Lakshmikumar, R. Hadaway, and M. Copeland, "Characterization and modeling of mismatch in MOS transistors for precision analog design," IEEE J. Solid-State Circuits, Vol. SC-21, p. 1057-1066, Dec. 1986.

- [19] N. Ahmed and T. Natarajan, Discrete-Time Signals and Systems, Prentice-Hall, Englewood Cliffs, NJ, 1983.

- [20] R. Steele, Delta Modulation Systems, Pentech Press, London, England, 1975.

- [21] N. Scheinberg and D. Schilling, "Techniques for correcting transmission error in video adaptive delta-modulation channels," IEEE Trans. Commun., p. 1064-1070, Sept. 1977.

- [22] Y. Matsuya, et al, "A 16 bit oversampling A-to-D conversion technology using triple-integration noise shaping," IEEE J. of Solid-State Circuits, Vol. SC-22, No. 6, pp. 921-929, Dec. 1987.

- [23] M. Rebeschini et al, "A high-resolution CMOS Sigma-Delta A/D converter with 320 kHz output rate," Proc. ISCAS, pp. 246-249, 1989.

- [24] J. C. Candy, "A use of double integration in Sigma-Delta modulation," IEEE Trans. On Communications, Vol. COM-33, No. 3, p. 249-258, March 1985.

- [25] R. Koch, et al, "A 12-bit Sigma-Delta analogto- digital converter with a 15-MHz clock rate," IEEE J. of Solid-State Circuits, Vol. SC-21, No. 6, pp. 1003-1010, Dec. 1986.

- [26] B. Boser and B. Wooley, "Quantization error spectrum of Sigma-Delta modulators," Proc. International Symposium on Circuits and Systems, pp. 2331-2334, June, 1988.

#### **Author Biography**

Walid Emar was born in Palestine. He received the Dipl.-Ing. (M.Sc.) degree in industrial electronics and the Dr.-Ing. (Ph.D.) degree in power electronics and control from the University of West Bohemia, Pilsen, Czech Republic. In 2001, he joined Škoda Transportation, Škoda Company, Pilsen, Czech Republic. In 2002, he joined Birzeit University, Electrical and Computer Department. Currently, He is now teaching at Al-Isra Private University as a full-time assistant professor. He is engaged in research and development of high power multilevel converters for industrial and traction applications, as well as dc/dc converters and controllers.